Trochę teorii o SPI

Interfejs SPI został opracowany przez firmę Motorola, jest jednym z najczęściej stosowanych interfejsów komunikacyjnych. Transmisja ma charakter Master-Slave i podobnie jak w I2C do magistrali można podpiąć kilka urządzeń typu master oraz slave. SPI nie ma ograniczenia dodawanych urządzeń, lecz ich liczba jest uzależniona od liczby dostępnych portów układu master oraz od pojemności, która może ograniczyć szybkość transmisji danych. W jednej chwili tylko jeden układ może inicjalizować komunikację. Typowa szybkość wymiany informacji wynosi 2,1 Mb/s, lecz specjalnie zaprojektowane układy mogą osiągać prędkości nawet do 10 Mb/s.

Magistrala interfejsu SPI posiada cztery linie sygnałowe: SCK (Serial Clock) odpowiada za taktowanie zegarowe co oznacza, że jest to interfejs synchroniczny. (SS) (Slave Select) odpowiada za wybór układu slave (brak adresów urządzeń) i może być generowany jedynie przez mastera. MISO (Master In – Slave Out) odpowiada za odbieranie informacji, a MOSI (Master Out – Slave In) za wysyłanie danych. Ze względu na fakt, że SPI posiada dwie linie danych master może jednocześnie nadawać i odbierać informacje. Budowa portów jest typu push-pull, zatem linie nie wymagają podciągnięcia do nacięcia zasilania za pomocą rezystorów. Typowe połączenie urządzeń komunikujących się za pomocą interfejsu SPI przedstawione jest na poniższym rysunku.

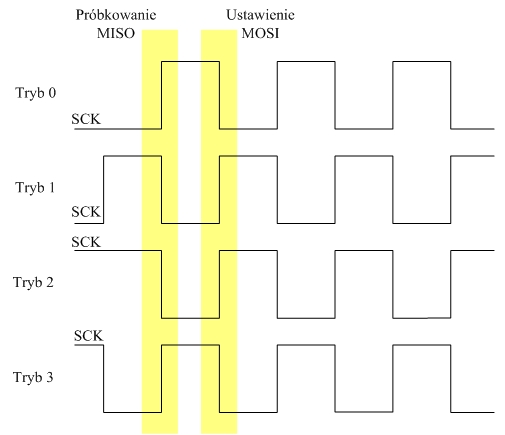

W interfejsie SPI wyróżnia się cztery tryby pracy, gdzie układy konfiguruje się pod względem momentu próbkowania. Tryb 0 i 3 charakteryzuje się tym, dane na linii MISO próbkowane są w momencie zbocza narastającego, a MOSI opadającego, lecz w trybie 0 stan spoczynkowy linii CLS jest niski, a w trybie 3 wysoki. Tryby 1 i 2 próbkują dane na liniach MOSI i MISO odwrotnie. Stan spoczynkowy linii CLK dla trybu 1 jest niski, a dla trybu 2 wysoki.

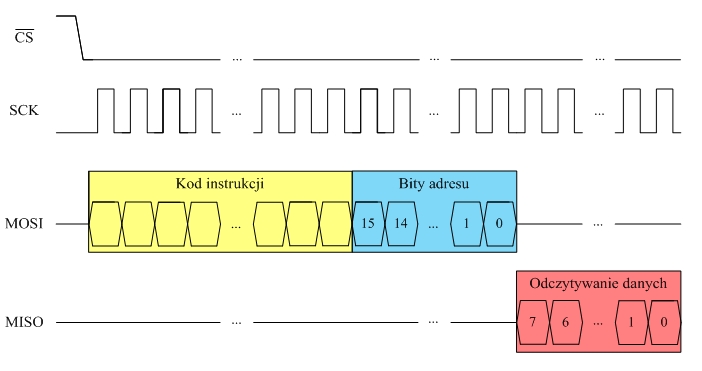

Ramka danych w interfejsie SPI może posiadać dowolną ilość bitów, lecz w zdecydowanej większości przypadków długość słowa wynosi albo 8, albo 16 bitów. W przypadku, kiedy do jednej magistrali zostanie przyłączonych kilku masterów, wówczas przed wysłaniem danych układy te badają zajętość linii SCK. Interfejs ten daje również możliwość wyboru, czy bity bardziej znaczące, czy mniej będą wysyłane/odbierane w pierwszej kolejność. Typową ramkę transmisji SPI przedstawiono na poniższym rysunku.