Na rozgrzewkę:

W tym wpisie zagłębimy się w elementy półprzewodnikowe, a konkretnie opiszę Ci zjawisko nazwane efektem Millera na podstawie tranzystorów MOSFET. Na początku przedstawię Ci pojemności pasożytnicze, następnie omówię Efekt Millera, oraz przekaże rady projektowe.

Zakres wpisu:

- Pojemności pasożytnicze w tranzystorze

- Efekt Millera

- Rady projektowe

Pojemności pasożytnicze w tranzystorze:

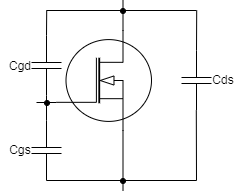

Zjawisko nazwane efektem Millera wynika z istnienia pojemności pomiędzy wyprowadzeniami tranzystora, które wynikają z jego budowy. Efekt Millera dotyczy jednej pojemności, bramka-dren Cgd.

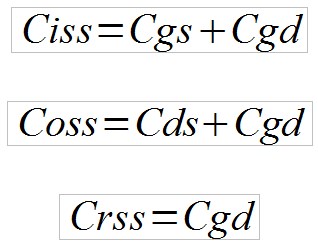

W dokumentacjach tranzystorów masz podane wartości pojemności wejściowej (Ciss), wyjściowej (Coss) oraz reverse transfer (Crss). Teraz zastanów się, które pojemności tworzą np. pojemność wejściową i jak te parametry są wyznaczane.

Już mówię, otóż:

- Wejściowa, składa się z pojemności bramka-źródło oraz bramka-dren, mierzona pomiędzy bramką, a źródłem, przy zwarciu zacisków dren-źródło dla sygnałów AC. Ma bezpośrednio wpływ na opóźnienia załączanie i wyłączania tranzystora.

- Wyjściowa, składa się z pojemności dren-źródło oraz bramka-dren, mierzona pomiędzy drenem, a źródłem przy zwarciu zacisków bramka-źródło dla sygnałów AC.

- Reverse transfer, składa się z pojemności bramka-dren, mierzona pomiędzy bramką, a drenem przy połączeniu źródła do masy.

Efekt Millera:

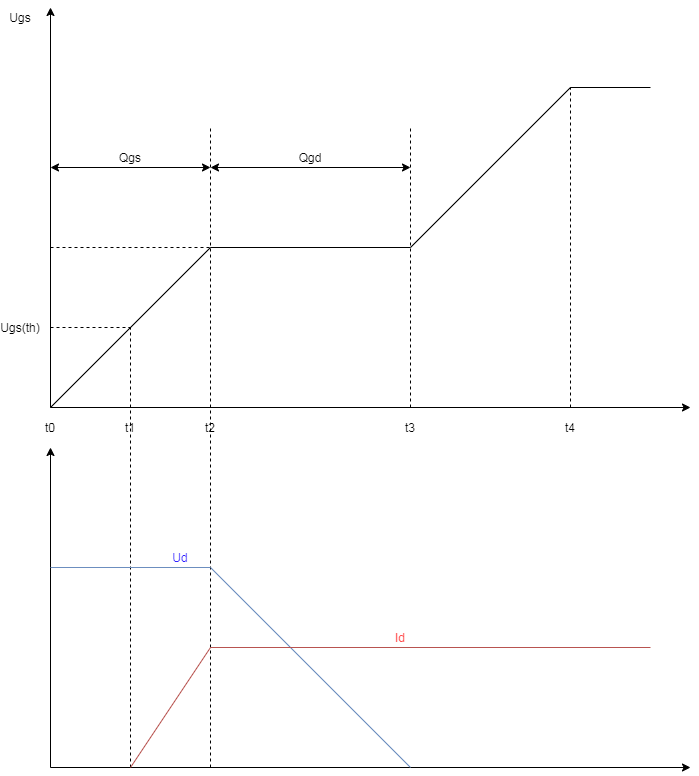

Efekt Millera i jego wpływ na załączanie tranzystora najlepiej zobrazować na przebiegu napięcia Ugs, napięcia Ud, oraz prądu Id względem czasu. W przedziale czasu t0-t2 ładowana jest pojemność Cgs, następnie w przedziale t2-t3 ładowana jest pojemność Cgd. Pojemność Cgd ładowana jest dłużej niż Cgs z powodu mniejszego prądu wynikającego ze zmniejszania napięcia drenu w czasie procesu załączania. Po naładowaniu obydwu pojemności napięcie Ugs narasta do napięcia zasilania, a tranzystor jest w pełni załączony, co widać na spadku napięcia Ud.

Efekt Millera - straty mocy tranzystora:

Jak widzisz z Rys. 3 pojemność Cgd wpływa na straty łączeniowe tranzystora wynikające z płynącego prądu, lecz jeszcze nie w pełni zamkniętego tranzystora. Łączeniowe straty mocy opisałem w jednym z wpisów.

Rady projektowe:

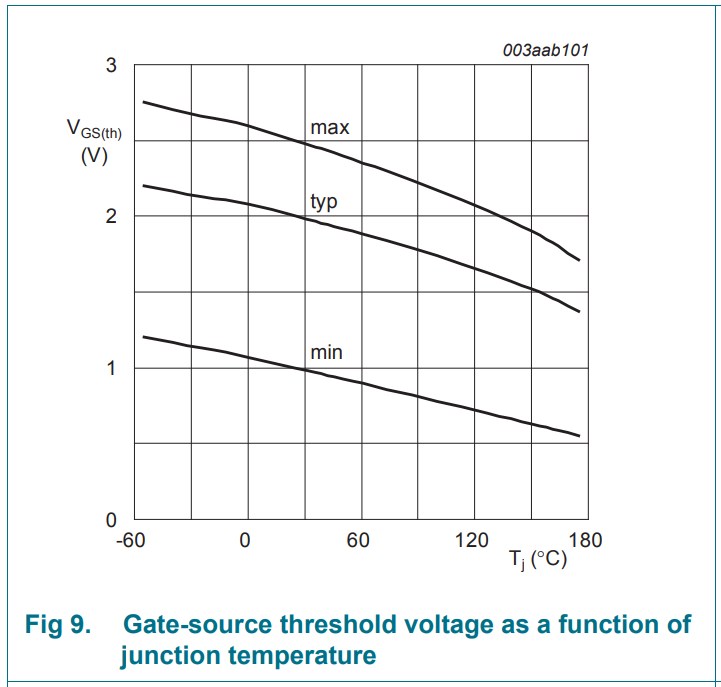

- Używaj rezystora lub drivera ściągającego potencjał bramki do napięcia źródła lub poniżej tego napięcia. Rada ta wynika z możliwości załączenia tranzystora na skutek zakłóceń lub szybkiego narastania napięcia na drenie poprzez pojemność Cgd. Należy o tym pamiętać w normalnych aplikacjach, a w szczególności w aplikacjach pracujących w wysokich temperaturach, gdyż napięcie Ugs(th) zmniejsza się wraz ze wzrostem temperatury, co przedstawiłem na Rys. 4.

[1] https://assets.nexperia.com/documents/data-sheet/2N7002.pdf

[2] https://www.infineon.com/dgdl/mosfet.pdf?fileId=5546d462533600a4015357444e913f4f